2026年 AIハードウェア展望:NVIDIA Rubinの「鶴翼」を突く競合アーキテクチャの全貌と生存戦略

この記事を読むと、Vera Rubinが打ち立てた“ラック統合”に、Groq LPU(実質アクアハイア)が低遅延推論の翼を継ぎ足し、学習から推論までを包囲する「鶴翼の陣」がなぜ完成するのかが腹落ちします。

そして2026年に確定したのは王座の交代ではありません。用途別に“勝ち筋が分岐”し、局地戦の主戦場に入った――その全体像(勢力図と勝ち筋のロジック)を、一気に掴めます。

この記事の結論:

- 王者のラックスケール最適化:Vera RubinがCPU、GPU、DPU、スイッチを含む6つのコンポーネントを完全に統合。Groqの低レイテンシ技術をも飲み込み、死角なき「鶴翼の陣」を完成させた。

- FLOPS信仰からの脱却:推論のボトルネックは演算ではなくデータ移動(Memory-bound)にある。カタログ上の演算性能(FLOPS)は、推論の実効効率を反映しない指標となった。

- 反乱同盟の五つの戦略:汎用性の贅肉を削ぎ落とした特化型ASIC(Etched)や、物理的に配線を消すウェハースケール(Cerebras)などが、特定のワークロードで王者の包囲網を突き抜ける。

1. 王者の絶対基準:Vera Rubinのラック最適化と「鶴翼の陣」の完成

Vera Rubinアーキテクチャとは、NVIDIAが提唱する「ラックこそが最小単位のコンピュータである」という思想を具現化したもので、演算、通信、制御の全てを単一システムとして最適化したAIインフラの決定版です。

6つの主要コンポーネントが奏でる「完璧な整合性」の快挙

2026年、NVIDIA Vera Rubinが他を圧倒している理由は、単に個々のチップが速いからではありません。演算、通信、制御の全てを担う以下の「6つの主要コンポーネント」が、ラック単位で完璧な整合性を持って設計されていることにあります。

① NVIDIA Vera CPU

- Arm互換のカスタム「Olympus」コアを88基搭載したCPU。

- 大規模AIファクトリーの制御・オーケストレーションやエージェント推論向けに最適化されたプロセッサです。

② NVIDIA Rubin GPU

- 224 SM、第6世代Tensor Core、最大288GBのHBM4(最大22TB/s帯域)を備える次世代アクセラレータ。

- 長コンテキストLLMやMoE(混合専門家)モデルの推論コストを大幅に下げることを狙った中核ユニットです。

③ NVIDIA NVLink 6 Switch

- 1GPUあたり3.6TB/sの双方向帯域を提供する第6世代スイッチ。

- NVL72ラック内の72 GPUを「一つの巨大GPU」のように全結合で動作させるスケールアップ・ファブリックです。

④ NVIDIA ConnectX-9 SuperNIC

- ラック外とのスケールアウト通信を担う高スループット・低レイテンシのNIC。

- Rubinシステムと他ラック、データセンター、クラウドを結ぶネットワークエンドポイントとして機能します。

⑤ NVIDIA BlueField-4 DPU

- Grace系CPUコアとConnectX-9を統合. ストレージやセキュリティ、インフラ処理をオフロードします。

- AI計算ノードを軽量化する「インフラ専用プロセッサ」です。

⑥ NVIDIA Spectrum-X Ethernet Photonics (CPO)

- コパッケージド・オプティクス(CPO)を全面的に採用した次世代スイッチ。1ポートあたり1.6Tb/sの超広帯域を実現。

- 複数のVera Rubin NVL72ラックを束ねてSuperPODレベルへ拡張する、AIファクトリーの神経系として機能します。

この異次元の統合に加え、NVIDIAは2025年12月24日、Groqの技術チームとIPを200億ドルで獲得(アクアハイヤ)しました。これにより、「巨大モデルを丸ごと呑み込むRubin(GPU)」と、「瞬発的なトークン生成に特化したLPU」という二段構えの布陣が完成。学習から推論まで全方位を包囲する「鶴翼の陣」は、今まさに完成を見ました。

補助翼:エッジという“もう一つの戦場”を固めるJetson Thor

データセンター側で「鶴翼の陣」が閉じた今、NVIDIAはもう一枚の翼――ロボティクス・モビリティ/エッジという現実世界の戦場も同時に強化しています。

Jetson Thorは推論を“現場”へ運ぶ主力であり、エッジ側の性能と採用が伸びるほど、王者の陣形は二正面で厚みを増す。だからこそ次章では、勝負が「王座交代」ではなく用途別の局地戦へ分岐する理由を解剖します。

2. なぜ今、AIハードウェアの「再定義」が必要なのか

王者がこれほどまでに完璧なラックスケール最適化を達成した今、なぜ私たちは「再定義」を語る必要があるのでしょうか。それは、NVIDIAが完成させた「汎用的な最強」が、特定の極限環境においては「回避不能なコスト(重税)」へと変貌しつつあるからです。

2.1 カタログスペックとしての演算速度(FLOPS)の衝撃

Rubinアーキテクチャが提示した数値は、従来の常識を破壊するものでした。特に新精度 $NVFP4$ の導入により、理論上の演算性能はBlackwell世代を遥かに凌駕しています。

| アーキテクチャ | 演算精度 | 演算性能 (PFLOPS) | メモリ帯域 (TB/s) |

|---|---|---|---|

| Vera Rubin (R100) | NVFP4 | 推論 50.0 / 学習 35.0 | 22.0 (HBM4) |

| Blackwell (B200) | FP4 | 20.0 | 8.0 (HBM3e) |

| Hopper (H100) | FP8 | 4.0 | 3.3 (HBM3) |

しかし、50 PFLOPSという圧倒的なパワーを目の前にして、エンジニアたちは気づき始めています。「この巨大な馬力が、実際の対話応答に100%変換されていない」という事実に。ここから再定義が始まります。

2.2 なぜ「FLOPS」は推論で嘘をつくのか:物理的限界の解剖

演算性能(FLOPS)が最強でも、推論が爆速にならない理由。それは、AIの学習と推論では、ハードウェア内で行われている物理的プロセスが根本的に異なるからです。

演算性能(FLOPS)が最強でも、推論が爆速にならない理由。それは、AIの学習と推論では、ハードウェア内で行われている物理的プロセスが根本的に異なるからです。

学習は「演算性能(Compute-bound)」に支配される

学習は、データを流し込み、誤差を元に重みを補正する「逆伝播(バックプロパゲーション)」の繰り返しです。ここでは複雑な行列演算が休みなく続くため、計算機の馬力(FLOPS)がそのまま戦闘力となります。まさに「印刷機」が紙を刷り上げるスピードの勝負です。

推論は「データ移動速度(Memory-bound)」に支配される

対して推論は、すでに決まった重みの上を直線的に通り抜ける「順伝播」のみです。複雑な計算は不要ですが、LLMの場合、次の1文字(トークン)を出すために、膨大なパラメータを毎回メモリから読み出す必要があります。推論では、演算器の速さより重み・KVキャッシュを運ぶ速度が支配的になりやすいのです。

2.3 真の推論評価指標:インファレンス・メトリクス 2.0

2026年、賢明なITリーダーたちはFLOPSを盲信するのをやめ、TTFTや実効利用率といった「実効指標」を重視し始めています。以下の比較表は、公開情報と各社アーキテクチャの特徴から編集部が描いた「典型的な傾向イメージ」であり、特定ベンチマークの実測値ではなく、意思決定のための概念マップと捉えてください。

結論:推論において真に重要なのは演算馬力ではなく、いかに隙間なくデータを供給し続けられるか(利用率)です。

| 評価軸 | NVIDIA Rubin | NVIDIA LPU | Etched Sohu | AMD MI400 | Google TPU v7 | Cerebras WSE-3 | SambaNova |

|---|---|---|---|---|---|---|---|

| TTFT (初動遅延) | 200ms〜 | 10ms〜 | 50ms〜 | 150ms〜 | 80ms〜 | 5ms〜 | 20ms〜 |

| 実効利用率 (MBU) | 約 35% | 約 95% | 約 98% | 約 45% | 約 65% | 約 85% | 約 90% |

| AI燃費 (T/J) | 普通 | 高い | 最高 | 普通 | 高い | 最高 | 高い |

| 真の武器 | 汎用性 | 低遅延 | 特化コスト | 巨大容量 | 自社最適化 | 超高速通信 | データフロー |

※数値はワークロード、量子化、バッチ、ネットワーク構成で大きく変動します。70B級は現在、企業の独自モデル構築において最も費用対効果が高い基準サイズです。

3. 王者の包囲網を突く、反乱同盟の「五つの生存戦略」

NVIDIAの完璧なラックスケール最適化が達成された今、競合他社が生き残る道はひとつしかありません。それは、NVIDIAが「すべての人に最高の環境を」提供するために背負った「汎用性の重税(Generality Tax)」から、特定のユースケースを解き放つことです。ここから、一点突破の「魚鱗(ぎょりん)の陣」による反撃が始まります。

① 「Transformer専用」による特化の暴力(Etched)

Etched Sohuなどは「Transformer以外の計算は物理的に行わない」という決断を下しました。NVIDIAが将来のモデル変化に備えて残した汎用回路をそぎ落とし、全面積をTransformer推論に振り切ることで、Etchedは「H100比20倍高速・低コスト」という攻めた主張を掲げています。実測の検証はこれからですが、「何でも切れる万能包丁(NVIDIA)」に対する「刺身しか切らない名刀(ASIC)」の戦略です。

② 「メモリ容量」による物理的な力押し(AMD)

AMD Instinct MI400は、NVIDIAがスピードを優先して犠牲にした「容量」で勝負を挑みます。公開情報ベースでは432GB級のHBM4を搭載すると報じられており、巨大モデルをできるだけ分割せずに載せ切る「物量作戦」で、ラックスケール前提のRubin戦略の急所を突きにきています。

③ 「自社専用」という究極の垂直統合(Google / AWS)

Google TPU v7やAWS Trainium 3は、自社クラウド内で自社のAIモデルを動かすためだけにチップを設計しています。彼らはNVIDIAの利益率を自社のコストから排除し、自社ワークロードにおいて「電力あたりの知能生成量」の極致に達しています。これは最大のバイヤーが最大の競合へ変わる、静かなる独立宣言です。

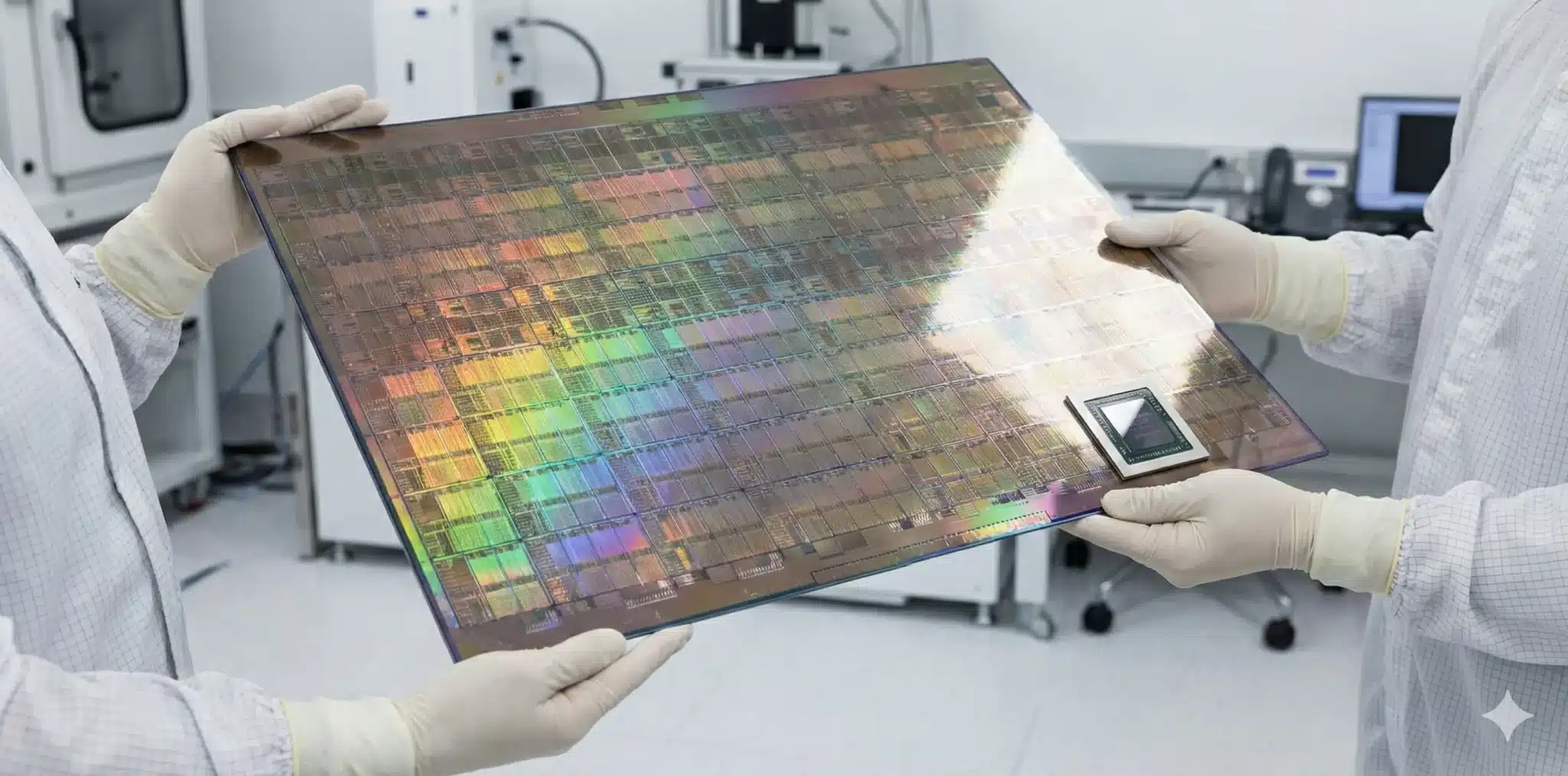

④ 「配線を消す」ウェハースケールの革命(Cerebras)

Cerebras WSE-3(および将来の後継機)は、小さなチップを並べるのではなく、シリコンウェハー1枚をまるごと1つのチップにするという狂気的なアプローチをとります。チップ間を繋ぐ「銅線」そのものを物理的に消し去り、光速のオンチップ通信のみで処理を行うことで、NVIDIAラックが直面する通信ボトルネックを異次元のレベルで解決しています。まさに「繋がないことによる速度」の追求です。

Cerebras WSE-3(および将来の後継機)は、小さなチップを並べるのではなく、シリコンウェハー1枚をまるごと1つのチップにするという狂気的なアプローチをとります。チップ間を繋ぐ「銅線」そのものを物理的に消し去り、光速のオンチップ通信のみで処理を行うことで、NVIDIAラックが直面する通信ボトルネックを異次元のレベルで解決しています。まさに「繋がないことによる速度」の追求です。

⑤ 「データフロー」によるボトルネックの粉砕(SambaNova / Tenstorrent)

SambaNovaやTenstorrentは、命令を順番に実行する従来のプロセッサ構造を捨て、データの流れに合わせてハードウェアを再構成する「データフロー・アーキテクチャ」を採用しています。これにより、推論時のバッチサイズが1(単一ユーザー)であっても、演算器を100%近い効率で回し続けることが可能です。

専門用語まとめ

- メモリーの壁 (Memory Wall)

- 演算器の処理速度に対し、メモリのデータ転送速度が追いつかず、システム性能がメモリによって制限される現象。

- Compute-bound (演算束縛)

- 計算処理が膨大で、演算器の能力が全体の限界を決めている状態。AIの「学習」フェーズがこれに当たる。

- Memory-bound (メモリ束縛)

- 計算自体は単純だが、データの読み書き速度が全体の限界を決めている状態. AIの「推論」フェーズの特性。

よくある質問(FAQ)

Q1. なぜ演算速度(FLOPS)が最強のNVIDIAが、推論で他社に負けることがあるのですか?

A1. 推論のボトルネックが「計算速度」ではなく「メモリからのデータ読み出し速度」にあるからです。NVIDIAのGPUはデータの到着を待つ「空回り」の時間が多いため、実効性能では特化ASICに及ばない場合があります。

Q2. Groqの技術を飲み込んだNVIDIAに、もはや死角はないのではありませんか?

A2. 確かに低レイテンシの弱点は埋まりましたが、NVIDIAは依然として「汎用チップ」です。特定モデルに特化したEtchedのようなASICと比べると、不要な回路や電力消費という「汎用性の重税」がコスト増として残ります。

Q3. 2026年、どのメーカーのチップが「買い」ですか?

A3. フロンティアモデルの学習ならNVIDIA Rubin一択です。しかし、特定のLlamaモデル等を大規模に、かつ安価に推論したい場合は、EtchedやGoogle TPU、あるいはメモリ容量に優れるAMDが合理的な選択肢となります。

まとめ

2026年、NVIDIAのビジネスがVera Rubinによって安泰であることは疑いようのない事実です。しかし、私たちが目撃しているのは「王座の交代」ではなく、「AIインフラの明確な分断(セグメンテーション)」の確定です。

CxO向け

- 「学習(資産)」にはNVIDIAを、コストが膨らむ「推論(運用)」には特化ASICや自社チップを検討する「ヘテロジニアス投資」へ舵を切ってください。

開発統括/リード向け

- 特定のモデルに依存するサービスでは、NVIDIA一極集中から離脱し、TCOを劇的に下げる特化型インフラの検証を優先すべきです。

実装担当向け

- CUDAに依存しすぎず、TritonやMojoなどのハードウェア抽象化に強い開発スタックを採用し、インフラの選択肢を常に保持してください。

落とし穴(1行):FLOPSの数値だけで推論基盤を選定すると、膨大な電気代とレスポンス遅延という「贅肉の重税」に苦しむことになります。

今日のお持ち帰り3ポイント

- 2026年のNVIDIAは6つのコンポーネントの完全統合により、全方位の「鶴翼の陣」を完成させた。

- 推論性能の正体はFLOPSではなく「メモリーの壁」をいかに無効化するかにある。

- 絶対王者の汎用性を逆手に取り、五つの生存戦略を持つ競合他社が、特定の局地戦で王者のコストを食い破っている。

主な参考サイト

- NVIDIA Newsroom: NVIDIA Rubin Platform and AI Supercomputing(2026)

- AMD Instinct シリーズ公式ページ(MI400/MI350)

- Google Cloud Blog: Trillium (TPU v6) and Ironwood Roadmap(2025)

- Etched: “Meet Sohu” 公式発表(LinkedIn)

- Cerebras: Chip / WSE 系列情報

合わせて読みたい

更新履歴

- 初版公開