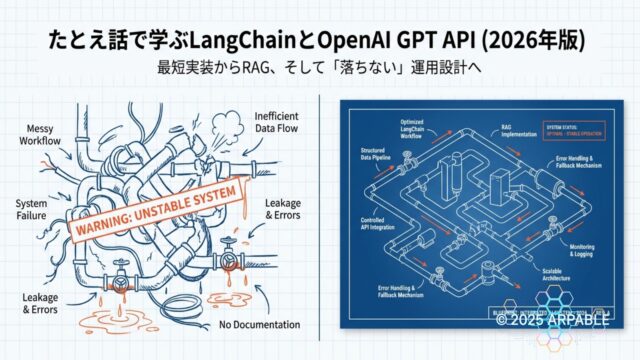

AIネットワーク三層|NVLink・InfiniBand・Ethernet/Spectrum-X【2025】

この記事を読むと三層アーキテクチャ(スケールアップ/アウト/アクロス)の全体像がわかり、目的に応じて最適なネットワーク(NVLink・InfiniBand・Spectrum-X/ブロードコム系Ethernet・光DCI)を選べるようになります。

この記事は、専門的な詳細に踏み込んだ技術解説記事です。

📌AIデータセンターネットワークの全体像や基本から学びたい方

➡NVLink vs Broadcom論争の真相|AIネットワークの力学を読み解く

📌LLMの基本的な仕組みや専門用語を学びたい方

➡初学者用LLM技術:NVLinkを理解するために【2025】

- 要点1:スケールアップはNVLink/NVSwitchでラック内をひとかたまりに

- 要点2:スケールアウトはIB(専用新幹線)/Ethernet(公共巨大鉄道)/Spectrum-X(AI特急)の選び分け

- 要点3:スケールアクロスは光DCI+渋滞制御(PFC/ECN/CNP)+配置最適

→ 詳しい比較は「第二部:スケールアウト」へ、戦略的視点は「第四部:業界構造」へ。

CxO/経営層向け:30秒で掴む戦略の核心

本記事の技術的な詳細に入る前に、経営判断に直結する3つのポイントをまとめます。

投資の優先順位:

まず「ラック内(スケールアップ)」の最適化が最優先です。ここに投資を集中させ、GPU間の通信ボトルネックを解消することが、AIファクトリー全体のROI(投資対効果)を最大化する鍵となります。

戦略的な選択:

次に「ラック間(スケールアウト)」のネットワークを「時間」で選ぶか「持続可能性」で選ぶかを決定します。導入リードタイム短縮(市場投入前倒し)を買うならInfiniBand、TCO最適化と既存人材の再利用を重視するならEthernetが基本戦略です。

未来への布石:

「データセンター間(スケールアクロス)」の接続は、将来の拡張を見据えた先行投資です。光技術(Optical DCI)への理解を深め、自社の地理的分散戦略と連携させることが重要になります。

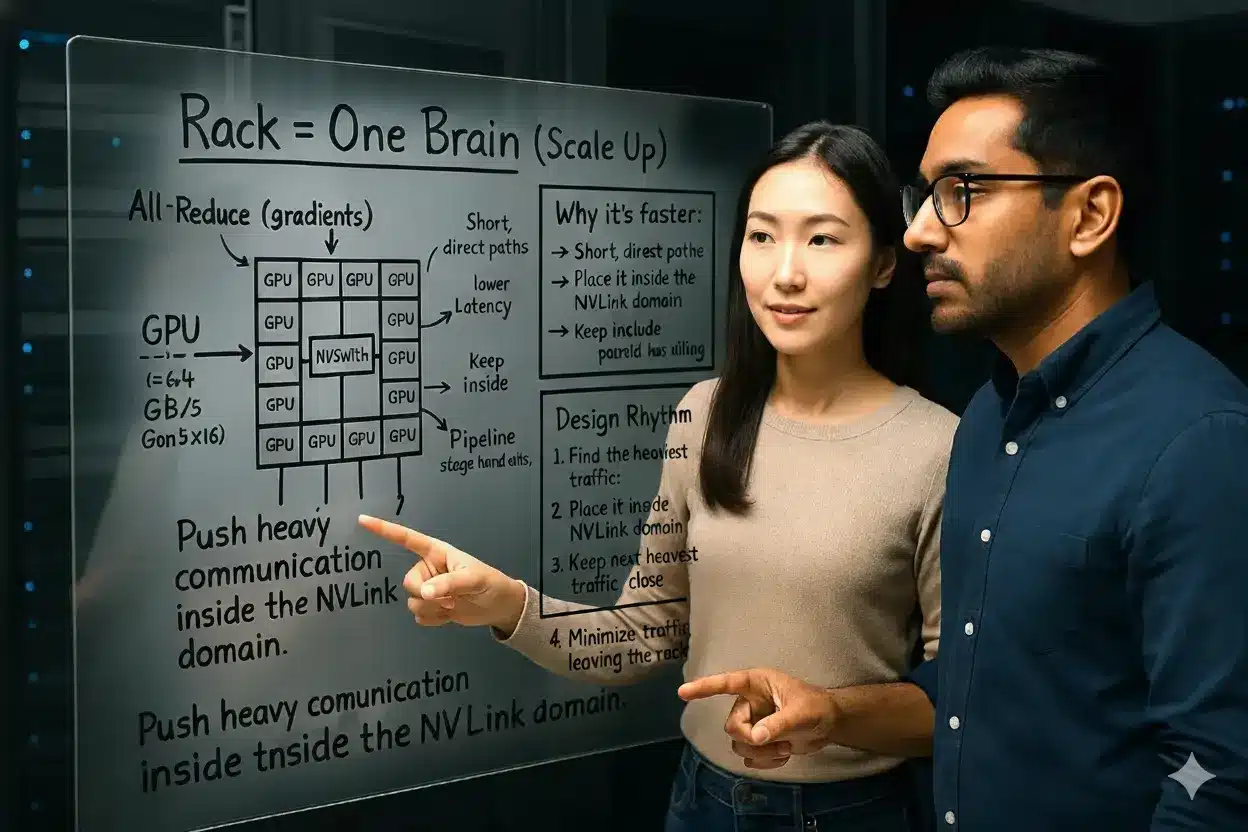

第一部(スケールアップの層):ラックの中を「ひとつの脳」に──NVLinkが担う中枢ネットワーク

要約:

ラック内のGPU群を“ひとかたまりの脳”のように動かすには、NVLink/NVSwitchで最も重い通信をラック内部に閉じ込め、帯域を太く・距離を短く・遅延を減らすことが絶対条件となります。通信待ちを抑える設計こそがスケールアップの肝です。

(続)前回、カフェでの何気ない会話からはじまった大学院生のエバとレオ、二人は場所を教室に移してAIデータセンターのネットワークを巡る地図を描き始めます。

ガラスボードの前に立つエバ。指し示した中央にNVLinkとNVSwitchの太いラインが描かれる――

エバ:「これがNVLinkとNVSwitchの役割よ。最も重い通信を見つけて、それをラックの内側に閉じ込めるの。」

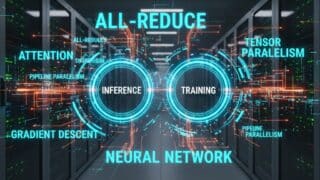

レオ:「テンソル並列での活性値受け渡し、パイプライン間の段データ転送、All-Reduceによる勾配集約――どれかが詰まれば全体が止まる。設計のリズムは単純だよ。」

- 最重通信はNVLinkドメイン(同一ラック)内に閉じ込める。

- 次に重い通信もできるだけ同じ階層・近接に集約する。

- 外へ出す通信は最小限にする。

エバ:「中で詰まりを消すことができれば、次章──“スケールアウト設計”が一気に楽になるわ。」

二人の視線の先、NVLinkとNVSwitchのネットワークは一つの脳の神経網のように輝いていた。

1) なぜGPU同士を高速でつなぐ必要があるのか?

深層学習の大規模な計算では、複数GPU間で膨大なデータをやり取りします。例えば、勾配の集約(All-Reduce)や中間活性の受け渡し(テンソル並列)、マイクロバッチの受け渡し(パイプライン並列)などで頻繁にGPU間通信が発生します。

GPU自体の高速化も重要ですが、GPU同士の通信が遅いと計算の待ちが生じ、「理論性能」を十分に活かせません。実際、分散計算では通信待ち時間の最小化が全体のスピード向上に直結するため、現代AIインフラ設計の最大のポイントとなっています。

計算処理を速くする以前に、「やり取り(通信)」をいかに速くするか。これがスケールアップに不可欠な鍵です。

📌深層学習の基本的な仕組みや専門用語を学びたい方はこちらの記事をご覧ください。

➡初学者用LLM技術:NVLinkを理解するために【2025】

2) どのくらい速いのか(PCIeとの肌感比較)

汎用のPCIeは便利ですが、帯域/遅延に限界があります。

(例:PCIe Gen5 x16 ≒ 64GB/s)

一方、NVLinkはGPUを複数レーンで直結し、1GPUあたり最大1.8TB/s(第5世代NVLink)の帯域まで拡張。更にNVSwitchによって「多対多同時通信」の混雑も一気に解消します。

例えでいえば、

PCIe=生活道路、NVLink=都市の太い動脈、NVSwitch=巨大ジャンクションです。

3) なぜ速いのか(技術のツボ)

AIインフラにおけるGPU間接続は、処理速度やスケーラビリティの要です。

NVLinkやNVSwitchは、低遅延・広帯域な通信と多対多接続を実現し、膨大なデータのやりとりと大規模モデルの効率的な分散処理を支えます。

- 直結で距離が短い → 遅延が非常に小さい。

- 多レーンで帯域が太い → 巨大なモデルの連続転送に強い。

- スイッチで多対多が一斉可能 → 多数GPUが順番待ちになりにくい。

この全てを組み合わせることで、NVLink/NVSwitch設計はAIインフラに不可欠な“神経網”となっています。

4) 何と何をつなぐのか(GPU↔GPU だけではない)

NVLinkは、GPU間の“最重通信”をラック内に閉じ込めて加速するスケールアップ・ファブリックです。第5世代NVLinkは1.8TB/s/ GPU(双方向)を実現し、NVLink Switchと組み合わせて多数GPUの同時多対多通信を可能にします。最新のGB200/GB300 NVL72では72基GPUが単一ドメインを形成し、総帯域130TB/sの低遅延オールトゥオール通信で大規模学習・推論をPCIe中心構成より高効率に駆動します。

● GPU ↔ GPU:

NVLinkで直結、NVLink Switchで多対多に拡張。NVL72のようなラック一体設計では、GPU群が“ほぼ一体の巨大GPU”として振る舞い、テンソル並列や大規模All-Reduceの待ちを最小化します。

● GPU ↔ CPU(Grace/Grace Hopperなど):

NVLink-C2Cにより現行(Grace)は900GB/s(双方向)でCPU–GPU/CPU–CPUをキャッシュコヒーレント接続。次世代(Vera, ロードマップ)では1.8TB/s(双方向)へ倍増見込み。

※次世代は計画情報で、仕様・時期は今後の更新に依存。

※)Tips1:

キャッシュコヒーレントとは? CPUとGPUがそれぞれ持つキャッシュの中身を自動的に一致させる仕組みで、同じデータを双方が見ても常に最新・正しい値になります。

※)Tips2:

GraceはNVIDIA製ArmサーバCPU。Grace HopperはGraceとHopper GPUを1モジュール化し、NVLink-C2CでCPU–GPUを900GB/sでコヒーレント接続。AI/HPCを高効率化。

● Intel連携(x86でもNVLink直結へ):

2025年9月18日(米国時間)、NVIDIAとIntelが共同開発・資本提携を公式発表。データセンター向けにNVIDIAカスタムx86 CPUをIntelが供給し、NVLinkで両アーキテクチャを連携させる方針が示された。具体仕様・量産時期は未公表のため、今後の続報で確定する。

● さらに(GPU/CPU以外も):

NVLink Fusionにより、他社CPUやカスタムAI ASICをNVLinkエコシステムに統合可能。ラック単位の標準アーキテクチャ上で、NVIDIA GPUやGraceに加え、ConnectX SuperNICやBlueField DPUと連携しながら用途別の半カスタム構成を柔軟に組めます。

5) 設計リズム(迷わない順番)

AIインフラでは、最も重い通信をNVLinkドメイン(同一ラック)に集約するのが定石です。通信階層を整理し、帯域最適化・遅延低減を先に固めれば、後段(スケールアウト)の設計が一気に楽になります。

- テンソル並列/パイプライン並列/データ並列のうち、最重通信を特定する。

- それをNVLink(直結)+NVLink Switch(多対多)の同一ドメインに閉じ込める。

- 次に重い通信も同一スイッチ階層・近接ブロックへ寄せる(トポロジーを崩さない)。

- 外へ出す通信(他ラック/他ポッド)は最小化──ここまで整うとNCCLの階層All-Reduceやシャーディング計画が素直に乗る。

※)Tips:

NUMA/トポロジーを意識し、GPU−CPU−NICの局所性(同一ベイ/同一スイッチ)を合わせると待ちが減ります。

6) つまずきやすいポイント

- 「PCIeでも十分」:規模が増すほど遅延が支配的になり、GPUが待機に入る。NVLinkドメイン外に重通信を出さない配置が重要。

- 「NVLinkがあれば自動で速い」:効果は並列方式の割付次第。テンソル並列は同一NVLinkドメイン、パイプライン段は近接、データ並列は階層All-Reduceを前提にブロッキング。

- スイッチ跨ぎの増加:NVLink Switchを不用意に横断すると実効帯域が低下。層/ブロック単位で通信を束ねることでホップ数と輻輳を抑制。

- NICの局所性を無視:外部ネットワーク(スケールアウト)へ出す経路は、同一ベイのNIC/スイッチに寄せてホットスポット化を防ぐ。

※)Tips:

バッチサイズや勾配蓄積の変更は通信/計算の重みを動かすため、並列方式の再最適化とセットで評価を。

7) 小さなまとめ(スケールアップのゴール)

NVLink/NVLink Switchでラック内の多数GPUを“ひとつの脳”に束ね、重通信を内側に閉じ込める──これがスケールアップの理想形です。十分な帯域・低遅延・トポロジー整備を先に固めることで、次章のスケールアウト(InfiniBand/Ethernet)設計はシンプルになります。

- ゴール:

ラック内を一体化し、重通信をNVLinkドメイン内で完結。 - 手段:

NVLink(直結)+NVLink Switch(多対多)で帯域を太く・距離を短く・待ちを減らす。 - 勘どころ:

最重通信の局在化と、スイッチ跨ぎ最小化、NUMA/局所性の確保。

エバ:「ラックの中をしっかりまとめ上げて初めて、“一つの意識”あるAI基盤が誕生する──NVLink/NVSwitch抜きに今や語れない領域ね。」

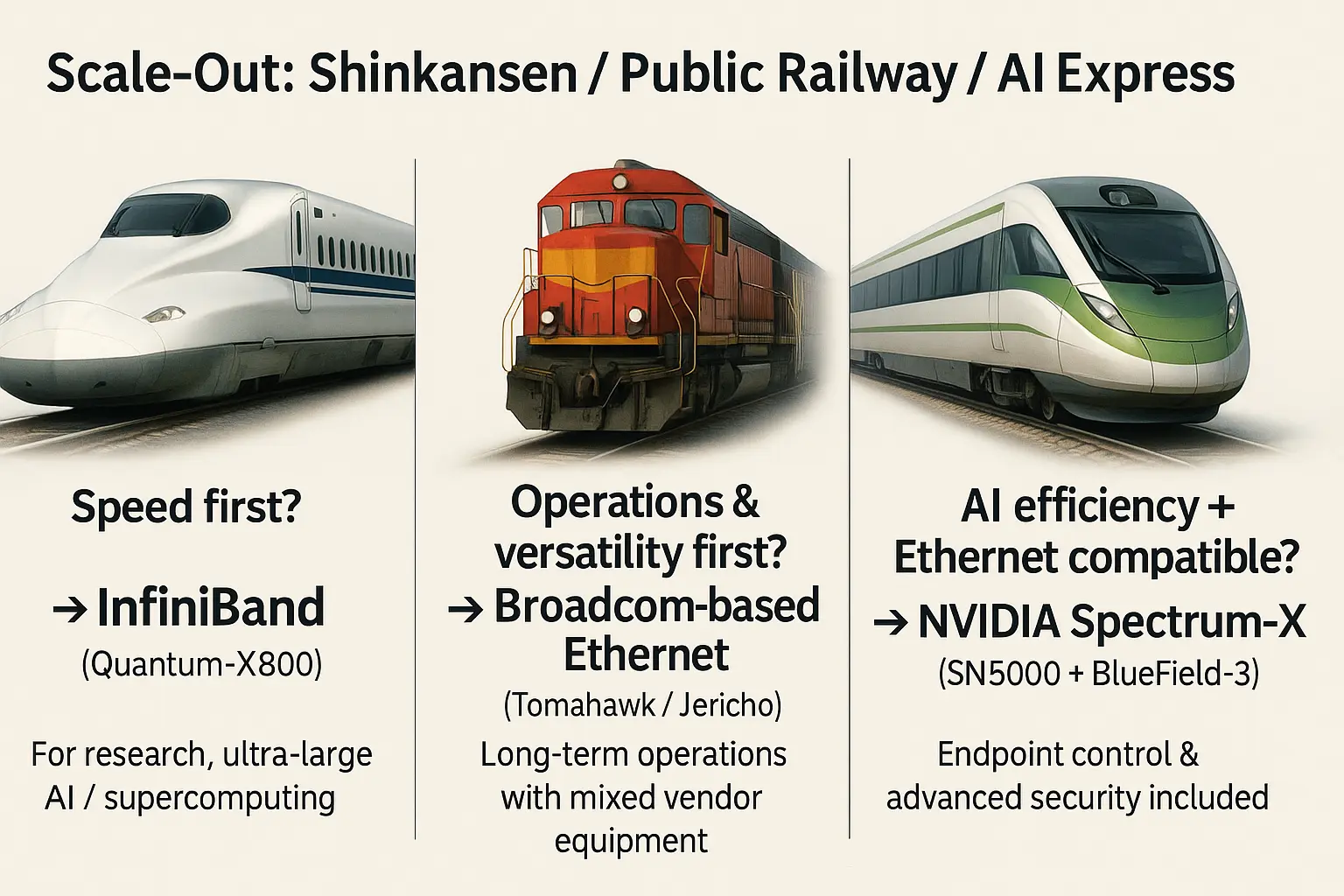

第二部:スケールアウトの路線選び――InfiniBand/Ethernet/Spectrum-X

要約:

専用新幹線=InfiniBand、公共巨大鉄道=Broadcom系Ethernet、AI特急レーン=Spectrum-X。

いずれも 800G世代 に到達。違いは「どこまで専用に振るか」「運用の幅をどう取るか」。ラック内を「脳」としたスケールアップ設計から、次は“多くのラック=工場”を協調させる帯域・遅延設計へ進みます。

比較条件:2025年時点の代表スイッチ(800Gb/s/ポート級)。AI学習の集団通信(All-Reduce/All-to-All)を想定し、一般的なClos 2段/3段を前提に“装置ベース(スイッチ1台)”で概算比較。

エバ:「ここからはスケールアウト。第1部で作った“ひとかたまりの脳”(NVLinkドメイン)を、ラック間でも足並みを揃えて次元を超えた計算工場に進化させるフェーズよ。」

レオ:「専用高速ならInfiniBand、運用資産や規模重視ならBroadcom系Ethernet、両者を柔軟に融合するならSpectrum-X、という選択肢になるんだ。」

“列車”のたとえで全体像を掴む

1) NVIDIA InfiniBand(Quantum-X800):専用新幹線

イメージ:AIクラスタ専用の完全予約制新幹線。決められた車両だけが一直線のレール上を低遅延・ロスレスで運行。到着時刻のブレが極小、同期通信も最速です。

代表スペック(装置ベース概算):総帯域:144ポート × 800Gb/s = 115.2 Tb/s(Quantum-X800、装置ベース)

※装置ベースの総和値であり、チップ性能ではありません。

2) Broadcom系 Ethernet(Tomahawk/Jericho):公共巨大鉄道

イメージ:特急・各停・貨物が共存する首都圏級の巨大鉄道網。誰でも使える公共インフラならではの柔軟さと規模が特徴。

代表スペック(装置ベース概算):例:64〜128 × 800GbE ≒ 約51〜102 Tb/s(筐体構成に依存)

3) NVIDIA Spectrum-X(SN5600+SuperNIC/DPU):AI特急レーン

イメージ:一般のEthernetにAI専用の特急レーンを重ねる新コンセプト。端点のBlueField-3 SuperNICが“AI車掌”となり輻輳を検知・制御、Spectrum-4スイッチと協調してAI用途に最適化します。

代表スペック(装置ベース):SN5600=64 × 800GbE = 約51.2 Tb/s

まとめ: 最短時間=InfiniBand|運用と規模=Ethernet|両立=Spectrum-X

| 評価軸 | InfiniBand(Quantum-X800) | Ethernet(Tomahawk 6採用スイッチ) | Spectrum-X(SN5600 ほか) |

|---|---|---|---|

| 路線の性格 | 専用新幹線 | 公共巨大鉄道 | AI特急レーン |

| 装置のポート総和(目安) | ≈ 115.2 Tb/s | 102.4 Tb/s(チップ)、筐体の有効ポート総和は実装構成による (例:64×800GbE など) |

≈ 51.2 Tb/s(64×800G) |

| 強み | 定時性・ロスレス・同期最短 | 規模・運用資産・マルチベンダ | 適応経路+端点DPU協調 |

| 使い分けの目安 | 最短の学習時間を取りに行く | 既存運用・規模・TCOを優先 | 両立(互換+AI最適化)を狙う |

凡例: 装置ベース=スイッチ筐体の有効ポート総和|チップベース=ASIC単体の理論スループット|NVLinkドメイン=NVL72等のラック内総帯域(本文は双方向表記で統一)。例:Quantum-X800=装置ベース、Tomahawk 6=チップ、GB300/GB200 NVL72=NVLinkドメイン。

注:本文と表は“わかりやすさ”重視で 装置ベース(スイッチ1台のポート総和) に統一。

参考までに「102.4 Tb/s/Chip」はASIC(チップ)単体値で、装置全体の帯域は実際のポート構成で決まります。

実務での選び分け(InfiniBand / Ethernet / Spectrum-X)

最短時間→InfiniBand/規模と運用→Ethernet/両立→Spectrum-X

用途・人材・既存資産・今後の成長戦略──どの指標を最重視したいかで最適路線は異なります。

スピード重視なら → InfiniBand(Quantum-X800)

- 研究・超大規模AI・スパコン系向け

運用資産&汎用性重視なら→ Broadcom系Ethernet(Tomahawk/Jericho)

- 異なるベンダー機器も活かし長期運用

AI効率+Ethernet互換なら → NVIDIA Spectrum-X(SN5000+BlueField-3)

- 端点帯域はSKU/世代で異なる:BlueField-3 SuperNICは最大400Gb/s、一方でConnectX-8/一部SuperNIC構成では最大800Gb/sまで対応。本文の装置総帯域はSN5600=64×800GbE(≈51.2Tb/s)を前提とする。

Key Takeaways(持ち帰りポイント)

- 最短時間を買うならInfiniBand(決勝戦仕様の専用新幹線)

- 運用資産と規模ならBroadcom Ethernet(公共巨大鉄道)

- AI効率/兼用ならSpectrum-X(AI特急レーン&DPU端点協調を重視)

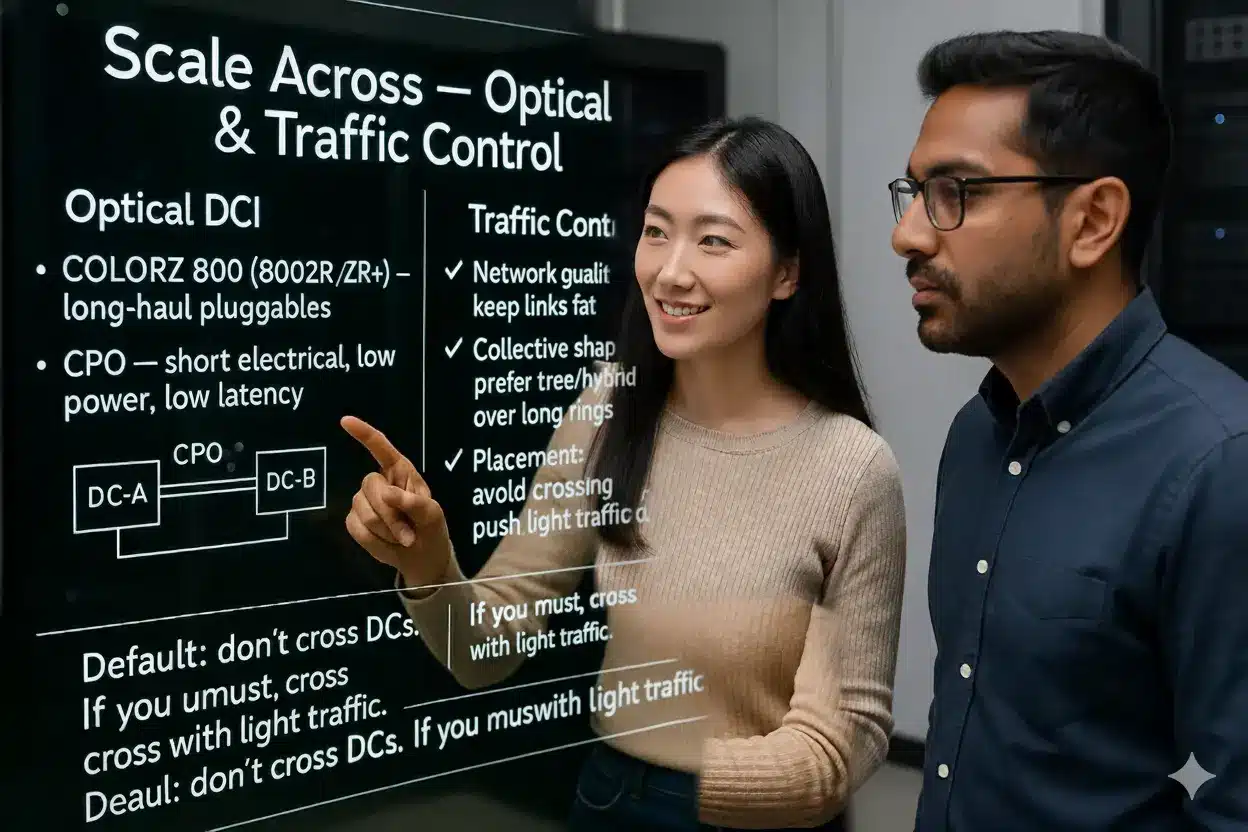

第三部(スケール・アクロスの層):都市と都市をつなぐ長距離ネットワーク──「DCI」と“光の橋”

要約:

遠距離は光DCIで太く結び、PFC/ECN/CNPで荷崩れを防ぎ、ノード/ラック/地域単位での集団通信と配置最適化を図る。「基本は“跨がない”設計」がDCスケールの要です。

エバ:「ここはScale Across。離れたデータセンター同士を光の橋(Optical DCI)で結び、AI学習の足並みを崩さないエリアへ進む区間よ。」

レオ:「ポイントは三つ。物理ネットワーク(DCI)の品質、集団通信(All-Reduce/All-to-Allなど)の組み方、そしてジョブやデータの配置。原則は“跨がない”設計で、跨がざるを得ない時は軽い通信を外側に寄せるのがコツだね。」

長距離は“光の橋”でつなぐ

- Marvell COLORZ 800(ZR/ZR+):

プラガブル光モジュールで800G級の長距離DCIを実現。専用トランスポンダ不要、ルータやスイッチに直接差すだけでメトロ〜リージョン間を“光の橋”として結びます。

- CPO(Co-Packaged Optics):

スイッチチップ真横で電気⇄光変換。電気配線が最小化され、超高密度・低消費電力・低遅延が三位一体で叶います。

- 光DSP(PAM4)×スイッチASIC:

MarvellのDSP+Teralynx 10(51.2Tbps)等により、大規模Closやメトロバックボーンを“太いまま”結びきる基礎体力。遠距離でも帯域ロスなくやり取りできる鍵です。

Ethernetで渋滞を起こさない“車間制御”

- PFC(Priority Flow Control):

優先度ごとに一時停止信号を出し、大事なサービスをドロップから守る。 - ECN(Explicit Congestion Notification):

輻輳したらパケットに“混雑マーク”をつけて減速させる仕組み。 - CNP(Congestion Notification Packet):

端点へ具体的な減速指示を送り協調的なトラフィック制御を実現。

これらをうまく設計/運用すれば、DC間でも荷崩れを抑制。実際、適応ルーティング+端点協調(Spectrum-X系)の設計により、NCCL All-Reduceの帯域効率改善を狙える構成。実効値はトポロジー/キュー設計/チューニングに依存する。

集団通信の形を変える(リングにこだわらない)

- リング型(Ring All-Reduce):

近距離で通信回数を抑えられるが、長距離跨ぎがあると「遅い道」を繰り返し通らざるを得ない。 - ツリー/ハイブリッド型:

幹線→枝線のイメージで、遅い区間の通過回数を減らす工程が可能。

ポイントは階層に合わせてプロセス/ノード/ラック/地域を最適配置し、遅いDCIリンクをできるだけ短く使うこと。ジョブスケジューラのアフィニティ設定も意外と効きます。

跨がない設計が基本(跨ぐ場合の置き方)

基本は同一DC内で閉じる。もし複数DCを跨ぐ場合は、通信の少ない並列化(例:データ並列)を外側に回し、頻繁な通信(例:テンソル並列・パイプライン並列)は同DC内に収める。データ湖やチェックポイントの設置先も“近い側”が基本。レプリケーション・再同期ポリシーも設計初期で決めておくと後が楽です。

ミニチェック(最初に見るべき3点)

- 片道遅延:NCCLの帯域が急降下する距離・サイズの閾値はどこか

- ロス率:短時間ピークのドロップやPFC異常が見受けられないか(テレメトリ/統計)

- 再送の波及:リトライがGPU待ち時間に波及していないか(プロファイラで確認)

Key Takeaways(持ち帰りポイント)

- 光で遠くを太く結ぶ(COLORZ 800、CPO、光DSP+大容量スイッチ)

- Ethernetの車間制御で荷崩れを防ぐ(PFC/ECN/CNP、広域最適化の併用)

- リング一辺倒にせずツリー/ハイブリッド通信で遅い区間の通過回数を最適化

- 基本は跨がない設計。跨ぐなら通信負荷の軽い方式を外側に回す

第四部:業界構造と戦略の深掘り

要約:技術の裏側にある各社の戦略と思惑を読み解きます。GPUの汎用性か、ASICの専門性か。垂直統合か、水平分業か。二つの大きな潮流が未来を形作ります。

XPUはGPUを食うのか?──対立ではなく“役割分担”

BroadcomやMarvellのカスタムASIC(XPU)が伸びると、GPUの出番は減るのでしょうか?答えは「ノー」です。GPUの強みは汎用性とCUDAエコシステム。学習から推論、科学計算まで“何でもこなせる”万能選手です。一方、ASICは専門職で、得意領域なら高効率ですが、応用は利きません。NVIDIA自身もNVLink Fusionを掲げてGPUとASICの共存を見据えており、今後は二者択一ではなく補完と分業が進むでしょう。

二つの潮流──Ethernet型とNVLink型、どちらも伸びる

未来のAIファクトリーは、二つの方向に分かれて進化します。一つは、超大規模データセンター。ここではコスト効率とスケールが最重視され、標準技術のEthernetが軸となります。もう一つは、国家主導のソビリンAIや、自動運転などフィジカルAIの世界。ここでは信頼性・安全性が絶対であり、NVLinkや最先端GPUの圧倒的性能が必須です。勝者総取りではなく、二つの世界が並行して伸びていくのです。

まとめ:意思決定は“時間”か“持続可能性”かで一本化する

スケールアップ(ラック内):NVLink/NVSwitchで同じラックのGPUをひとかたまりの脳として動かす。最も重い通信からNVLinkの内側に押し込むことが鉄則です。

スケールアウト(ラック間):都市間交通をどう敷くかが学習時間を左右します。専用新幹線=InfiniBandは最短時間を狙え、公共の超巨大鉄道=ブロードコム系Ethernetは運用資産と規模のしなやかさが強みです。

スケールアクロス(DC間):遠距離は光の橋でつなぎ、ネットワークの制御とジョブの配置を最適化することで、地理的な制約を超えていきます。

導入順序はシンプルです。①最重通信をNVLink内に閉じ込める → ②事業戦略でIBかEthernetかを選ぶ → ③将来の拡張に備え光DCIと配置ルールを決める。この順番で考えれば、複雑なAIネットワークの設計も、きっと迷うことはありません。

専門用語まとめ

- NVLink / NVLink Switch

- GPU同士を専用の直結配線で結ぶ技術と、その多対多切替ハブ。帯域を太く、遅延を短くでき、テンソル/勾配/パイプラインなどの重い通信をラック内で完結させやすい。

- キャッシュコヒーレント

- 複数のキャッシュが同じメモリ内容を矛盾なく保つ仕組み。GPUとCPU(Graceなど)をNVLink-C2Cで結ぶと、余分なコピーなしに一貫性ある読み書きができる。

- PFC / ECN / CNP

- Ethernetの混雑制御。PFCは優先度ごとの一時停止、ECNは混雑マーキング、CNPは端点へ減速指示を返す。長距離でもパケットの“荷崩れ”を抑える基礎。

- DCI(Data Center Interconnect)

- データセンター間を結ぶバックボーン。コヒーレント光やCPO、プラガブル光モジュール(例:COLORZ 800)で遠距離を高帯域・低消費電力で接続する。

- In-Network Computing(InfiniBand)

- スイッチ自体が和・平均などの部分集計を肩代わりし、往復トラフィックを削減する仕組み。InfiniBandの世代で継承され、All-Reduce等の集約通信を高速化する。

- 深いバッファ(Jericho)

- スイッチの大容量バッファで瞬間的な輻輳を吸収し、ドロップを最小化する設計。混雑の波及(フローの巻き込み)を抑え、長距離・高負荷時の安定性を高める。

- 適応ルーティング(Spectrum-X)

- パケット単位で経路を動的に選択し、ファブリック全体の利用率を最適化する技術。端点DPUと連携してホットスポット化や長いキュー滞留を防ぎ、スループットとジッタを改善する。

よくある質問(FAQ)

Q1. NVLinkドメインはどこまで広げるべきですか?

A1. 製品世代と構成に依存します。原則は最重通信がNVLink内で完結する粒度です。無理に外へ出すほど、外側の路線(IB/Ethernet)が律速になります。

Q2. EthernetだけでAI学習は十分に速くなりますか?

A2. 設計と運用次第で十分速くなります。Tomahawk/Jerichoの器を使い、適応ルーティングや端点協調(Spectrum-X系)を活かすと、実効帯域を底上げできます。

Q3. DC間を跨ぐAll-Reduceが遅いのはなぜ?対策は?

A3. 遅延とロスの複合要因で、リングだと遅い区間を何度も通るため。ツリー/ハイブリッドへ切り替え、PFC/ECN/CNPを正しく調整し、配置を階層化してください。

Q4. CxOは何を指示すべきですか?

A4. まず買うのは時間か持続可能性かを一本化。次にNVLink最適化を前提条件とし、路線(IB/Ethernet/Spectrum-X)と光DCIの導線、“跨がない”配置ルールを決めることです。

主な参考サイト

- NVIDIA Quantum-X800 InfiniBand Switches(2025)

- Broadcom Tomahawk 6(102.4Tb/s)製品ページ(2025)

- Broadcom Jericho/DNX:HyperPortsと深いバッファ(2025)

- NVIDIA Spectrum-X / Spectrum-XGS(2025)

- Marvell COLORZ 800(800ZR/ZR+)公式(2025)

合わせて読みたい

- NVLink vs Broadcom論争の真相|AIネットワークの力学を読み解く(入門用ハブ記事)

- NVIDIA NVLink Fusion発表|AIチップ市場の新展開

- AI最前線!NVIDIA CEO講演解説

- AIが金を掘る時代へ:NVIDIA GTC 2025が示したトークン採掘の未来

- AIインフラ市場2025最新|NVIDIA独占に挑む各社戦略

- AIチップ覇権戦争2025: NVIDIAの銀河系戦略に挑む反逆者たち

- Oracle Cloud AI戦略:タイタンの賭けと「Stargate」が拓くAIキングメーカーへの道

- AIインフラ戦争2025|NVIDIA×OpenAI・45兆円契約の全貌

- 2025年上半期 総まとめ:AI社会実装を決定づけた4大トレンド

更新履歴

- 初版公開